# Logic Operations of Chemically Assembled Single-Electron Transistor

Kosuke Maeda,<sup>†,⊥</sup> Norio Okabayashi,<sup>†,⊥</sup> Shinya Kano,<sup>†,⊥</sup> Shuhei Takeshita,<sup>†,⊥</sup> Daisuke Tanaka,<sup>‡,⊥</sup> Masanori Sakamoto,<sup>‡,⊥</sup> Toshiharu Teranishi,<sup>§,⊥</sup> and Yutaka Majima<sup>†,⊥,¶,\*</sup>

<sup>†</sup>Materials and Structures Laboratory, Tokyo Institute of Technology, Yokohama 226-8503, Japan, <sup>‡</sup>Graduate School of Pure and Applied Sciences, University of Tsukuba, Tsukuba 305-8571, Japan, <sup>§</sup>Institute for Chemical Research, Kyoto University, Uji-shi, Kyoto 611-0011, Japan, <sup>⊥</sup>CREST-JST, Yokohama 226-8503, Japan, and <sup>¶</sup>Department of Printed Electronics Engineering, Sunchon National University, Sunchon 540-742, Korea

anodevices such as single-electron transistors (SETs) have been studied extensively because of their potential low power consumption, high charge sensitivity, and multigate logic operation.<sup>1-7</sup> Tucker proposed the replacement of field effect transistors (FETs) with SETs in complementary-type logic gates,<sup>8</sup> where a logic gate composed of SETs would be smaller in size than a logic gate composed of the same number of FETs, owing to the small size of the individual SETs. The total number of SETs required for the logic operation can be decreased even further if the following beneficial features of the SET are considered: (1) the SET current oscillates as a function of the gate voltage and (2) in a double-gate SET, the phase of Coulomb oscillation shifts as a function of a linear combination of the two gate voltages. On the basis of these features, it would be possible to achieve the exclusive OR (XOR) gate operation of a single SET with a double-gate structure by using silicon technology<sup>9-11</sup> or carbon nanotubes (CNTs);<sup>12</sup> this is contrary to the case of a complementary-type XOR gate composed of 16 FETs. However, SETs have double-barrier tunneling junctions with Coulomb islands and gates, and therefore, there is a high demand for establishing methods for fabricating SETs that would give a precise device structure and have high process yield and high stability. Chemical assembling is a candidate method for fabricating nanodevices with precise structures on a subnanometer scale. Recently, we fabricated SETs in parallel composed of electroless gold-plated nanogap electrodes and chemisorbed chemically synthesized gold nanoparticles (NPs) by chemical assembling.<sup>13–15</sup>

In this paper, we demonstrate stable XOR and not exclusive OR (XNOR) operations of the chemically assembled SET with double side gates. We also demonstrate NOR, AND, OR,

## ABSTRACT

Double-gate single-electron transistors (SETs) were fabricated by chemical assembling using electroless gold-plated nanogap electrodes and chemisorbed chemically synthesized gold nanoparticles. The fabricated SET showed periodic and stable Coulomb oscillations under application of voltages of both gates. The sole SET also exhibited all two-input logic operations—XOR, XNOR, NAND, OR, NOR, and AND—with an on/off ratio of 10<sup>2</sup>. This demonstrates the potential of chemical assembling to give highly stable SETs exhibiting all logic operations.

**KEYWORDS:** single-electron transistor · bottom-up process · self-assembly · nanoparticle · nanogap electrode · logic operation

and NAND operations of the SET. Finally, we discuss the effectiveness of chemical assembling for the fabrication of the SETs in terms of achieving ideal SET properties and structure.

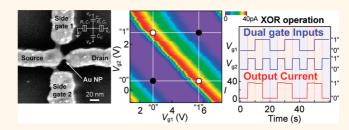

Figure 1a shows a scanning electron microscopy (SEM) image of fabricated SET with two side gates. A schematic illustration of a fabricated SET is shown in Figure 1b. White bright spots represented as decanethiol-protected Au NP<sup>16</sup> (core diameter of  $6.2 \pm 0.8$  nm) and single Au NP was chemisorbed *via* decanedithiol<sup>17,18</sup> between electroless goldplated nanogap electrodes,<sup>19</sup> which worked as a Coulomb island of SET. Double-gate electrodes were capacitively coupled equally to the Coulomb island, which is located in the center of side gate 1 and 2 electrodes.

## **RESULTS AND DISCUSSION**

We characterized the electron transport properties of the fabricated SET under the \* Address correspondence to majima@msl.titech.ac.jp.

Received for review January 21, 2012 and accepted February 26, 2012.

Published online February 27, 2012 10.1021/nn3003086

© 2012 American Chemical Society

VOL.6 • NO.3 • 2798-2803 • 2012

2798

Figure 1. (a) SEM top-view image of chemically assembled double-gate SET comprising gold nanogap electrodes and a gold nanoparticle. Equivalent circuit (inset).  $R_1$  is the resistance of the tunneling junction between source and Au NP (junction 1),  $C_1$  is the capacitance of the junction 1,  $R_2$  is the resistance of the tunneling junction between Au NP and drain (junction 2),  $C_2$  is the capacitance of the junction 2.  $C_{g1}$  ( $C_{g2}$ ) is the gate capacitances between side gate 1 (2) and Au NP. (b) Schematic illustration of an SET in which a gold nanoparticle is chemisorbed between the nanogap electrodes.

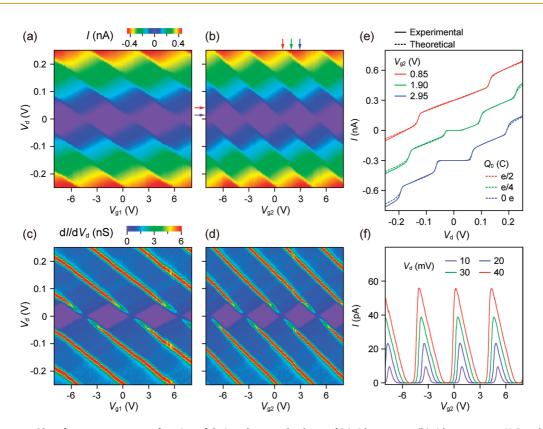

modulation of each side gate at a temperature of 9 K. Further, we plotted the experimentally determined tunneling current (I) of the device as a function of the drain voltage ( $V_d$ ) and the bias voltage of side gate 1 (hereafter gate 1) ( $V_{g1}$ ), which is the so-called stability diagram (see Figure 2a). Figure 2b shows the experimental stability diagram for the voltage of side gate 2 (hereafter gate 2) ( $V_{q2}$ ). Both these stability diagrams show Coulomb blockade regions (Coulomb diamonds) present at regular intervals along the lateral axis, where the heights of all diamonds in a particular diagram were nearly equal, as were the widths. Figure 2 panels c and d show the differential conductances  $(dI/dV_d)$  of these stability diagrams, derived by the numerical differentiation of the plots in Figure 2 panels a and b, respectively, where we can see the Coulomb diamonds more clearly. In Figure 2c,d, the stability diagrams in the  $dI/dV_d$  plots exhibit simple periodic patterns of Coulomb diamonds against  $V_{q1}$  and  $V_{q2}$  axes. It notes that, if plural NPs are introduced between nanogap electrodes, these simple periodic Coulomb diamonds are not observed. In the experiments, we prepared 157 SETs on the substrate. Fourteen perecent of SETs (22 out of 157 SETs) showed the Coulomb diamonds based on the single NP as the Coulomb island.

From the slope of the Coulomb diamond in the dl/dV<sub>d</sub> plot, we estimated the following:  $C_1 = 1.36 \text{ aF}$ ,  $C_2 = 1.22 \text{ aF}$ ,  $C_{g1} = 0.028 \text{ aF}$ , and  $C_{g2} = 0.038 \text{ aF}$ ; from these values, the charging energy<sup>20</sup> is given as  $E_C = e^2/2(C_1 + C_2 + C_{g1} + C_{g2}) = 30 \text{ meV}$ . It is noteworthy that the  $C_1$  and  $C_2$  values estimated from the stability diagram of  $V_{g1}$  are identical to those of  $V_{g2}$ . On account of the geometrical layout of the Au NP (Coulomb island), the source/drain electrodes, and gate  $1/_2$  electrodes, the capacitance of gate 1 ( $C_{g1}$ ) differs slightly from that of gate 2 ( $C_{g2}$ ). However,  $C_{g1}$  and  $C_{g2}$  are sufficient to achieve a logic operation under bias

voltages of the two input gates. Figure 2e shows the experimentally determined  $I - V_d$  characteristics for  $V_{q2}$ of 0.85, 1.90, and 2.95 V (solid lines). For comparison, this figure also shows theoretical  $I-V_{\rm d}$  curves obtained by the Orthodox theory at different values of fractional charge ( $Q_0$ ), from which we get  $R_1 = 10 \text{ M}\Omega$  and  $R_2 =$ 510  $\mathrm{M}\Omega.^{21-23}$   $\textit{V}_{q2}$  values of 0.85, 1.90, and 2.95 V correspond to  $Q_0$  values of e/2, e/4, and 0, respectively (dashed lines).  $Q_0$  is calculated as -0.3e (=(2.95 V) imes $C_{q2}/e - 1$ ). It notes that the value of  $Q_0$  is very stable and maintained through all of the experiments. The fairly good agreement between the theoretically and experimentally determined curves also suggests that the single Au NP contributes to the current flow between the source and drain electrodes. As  $R_2$  is much larger than  $R_1$  ( $R_2/R_1 = 51$ ), the  $I - V_d$  characteristic becomes asymmetric at  $V_{g2} = 1.9$  V around  $V_d = 0$  as shown in Figure 2e. The onsets of a step increase and a linear increase in current were observed at negative and positive voltages, and have been explained by the change in the excess number of electrons on the NP (N) and the overcoming the Coulomb blockade of  $C_{1}$ , respectively.<sup>21-23</sup>

Figure 2f shows the experimental  $I-V_{q2}$  characteristics for the  $V_{\rm d}$  values indicated by the horizontal arrows in Figure 2b; we can see the ideal Coulomb oscillation in Figure 2f. An asymmetric Coulomb oscillation peak is observed. The steep positive slope and the gradual negative slope are also explained as the change in N and the overcoming the Coulomb blockade of  $C_1$ , respectively.<sup>21–23</sup> It has been reported that an SET having only one metallic Coulomb island can exhibit ideal Coulomb oscillations, where a constant on-current flows periodically and the off-current (i.e., 0 A) owing to the Coulomb blockade also flows periodically.<sup>24–27</sup> However, this is not the case with SETs fabricated using silicon technology<sup>9-11</sup> or CNTs<sup>4,12</sup> or with SETs containing multiple Coulomb islands, since these islands contribute to the tunneling process.<sup>28–30</sup>

The electrical properties of the SET as shown in Figure 2 remain stable for over a week, which implies that its tunneling parameters, that is,  $R_1$ ,  $R_2$ , and  $Q_0$ , are extremely stable at 9 K. If the charge were to be trapped around the Coulomb island during the measurement, the stability diagram would not be observed clearly. As shown in Figure 2c,d, Q<sub>0</sub> of the Au NP varies with  $V_{a1}$  and  $V_{a2}$  without any distortion or hysteresis within the gate voltage range of -8 to 8 V. Such exceptionally stable properties are one of the key advantages of our chemically assembled SETs. This stability is explained as follows. The surface of the electrodes is covered with alkanethiol SAMs; alkanethiol also constitutes the ligand molecules of the Au NP, and the Au NP is chemisorbed to the source and drain electrodes by alkanedithiol molecules. Furthermore, the two tunneling barriers between the Au core of the NP and the

Figure 2. Plot of output current as a function of drain voltage and voltage of (a) side gate 1 or (b) side gate 2, at 9 K. Panels c and d show differential conductance plots derived from panels a and b, respectively, by numerical derivation. (e) Experimentally determined  $I-V_d$  curves for different voltages of side gate 2 indicated by the vertical arrows in panel b (solid lines). The dashed lines show theoretical  $I-V_d$  curves obtained by a conventional theory at different values of fractional charge ( $Q_0$ ). (f)  $I-V_{q2}$  curves for different drain voltages indicated by the horizontal arrows in panel b.

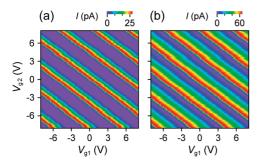

Figure 3. Plot of 2D output current versus bias voltages of side gates 1 and 2, at drain biases ( $V_d$ ) of (a) 25 and (b) 45 mV.

source/drain electrodes are made of alkanethiol and alkanedithiol molecules. These alkanethiol and alkanedithiol molecules are stable as electrical insulating materials, because of which the formed Coulomb diamonds exhibit ideal properties without any distortions or hysteresis (Figure 2). Then, because of this advantage, we were able to thoroughly measure the SET properties and demonstrate the logic operation, as described below.

In the double-gate SET, the phase of the Coulomb oscillation shifts with a change in  $V_{g1}$  and  $V_{g2}$  individually. Figure 3 panels a and b show experimental 2D-output current characteristics of the double-gate SET as a function of  $V_{g1}$  for different  $V_{g2}$  at drain biases of 25 and 45 mV, respectively. In these two figures, the areas

shaded in purple and other colors correspond to the regions in which Coulomb blockade is maintained (corresponding to device stability) and broken, respectively. On the basis of the oblique pattern of the rainbow stripes as seen in the 2D-output current characteristics, the phase of the Coulomb oscillation is expressed by a linear combination of  $V_{g1}$  and  $V_{g2}$ . The slope of the rainbow stripes is given by the ratio  $C_{g1}/C_{g2}$ ,<sup>9</sup> and is estimated as 0.74. As shown in Figure 3b, this ratio is independent of  $V_d$  (25 and 45 mV). The stability regions for  $V_d = 45$  mV are smaller than those for  $V_d = 25$  mV, which is also in agreement with the conventional theory.

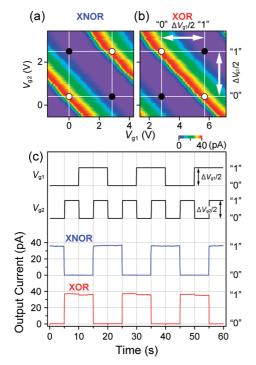

The 2D-output current characteristics of the doublegate SET enable the various logic operations. As shown in Figure 2,  $C_{g1}$  and  $C_{g2}$  are estimated as 0.028 and 0.038 aF, respectively, and the Coulomb oscillation spacing for  $\Delta V_{g1}$  (= $e/C_{g1}$ ) and  $\Delta V_{g2}$  (= $e/C_{g2}$ ) are 5.7 and 4.2 V, respectively. Figure 4a shows the 2D-output current characteristics at  $V_d$  = 30 mV. From this figure, it can be seen that the maximum current (red regions) of 37 pA flows at ( $V_{g1}$ ,  $V_{g2}$ ) of (0, 0.40 V); this current corresponds to the point when the normalized linear combination of the bias voltages of both gates, m (=  $V_{g1}/\Delta V_{g1}$  + ( $V_{g2} - V_{g2}'$ )/ $\Delta V_{g2}$ ), becomes an integer, where  $V_{g2}'$  is 0.40 V. This maximum current also flows when ( $V_{g1}$ ,  $V_{g2}$ ) becomes ( $\Delta V_{g1}/2$ ,  $V_{g2}'$  +  $\Delta V_{g2}/2$ ), since

VOL.6 • NO.3 • 2798-2803 • 2012

JAI

www.acsnano.org

Figure 4. Plot of 2D output current for half Coulomb oscillation squares versus  $V_{g1}$  and  $V_{g2}$  for (a) XNOR and (b) XOR operations at  $V_d = 30$  mV. The open circles (37 pA) and closed circles (0.2 pA or less) represent the combination of the gate operation points. (c) The logic operation of XNOR and XOR gates for two input pulses. In the case of XNOR operation, the height of the input pulse voltage for gate 1 (2) is  $\Delta V_{g1}/2$  ( $\Delta V_{g2}/2$ ) and the origin point (both input levels are low ("0")) of ( $V_{g1}$ ,  $V_{g2}$ ) is (0, 0.40 V). In the case of XNOR operation, the origin point of ( $V_{g1}$ ,  $V_{g2}$ ) is ( $\Delta V_{g1}/2$ , 0.40 V), and the height of the input pulse voltage for gate 1 (2) is  $\Delta V_{g1}/2$  ( $\Delta V_{q2}/2$ ).

*m* becomes 1. On the contrary, *m* becomes 0.5 at  $(V_{g1}, V_{g2}) = (0, V_{g2}' + \Delta V_{g2}/2)$  or  $(\Delta V_{g1}/2, V_{g2}')$ , which corresponds to the condition of Coulomb blockade being unbroken (purple area in Figure 4a) and an output current of 0.

The XNOR operation is achieved by applying the combination of two  $V_{g1}$  input levels, 0 V and  $\Delta V_{g1}/2$  as "0" and "1," and two  $V_{g2}$  input levels,  $V_{g2}'$  and  $V_{g2}' + \Delta V_{g2}/2$  as "0" and "1," respectively, which is the half Coulomb oscillation square of  $(V_{g1}, V_{g2})$  (see white square in Figure 4a). This operation is shown in Figure 4c (blue solid line); here, the  $(V_{g1}, V_{g2})$  input levels of (0, 0) and (1, 1) give an "on" current of 37 pA, and  $(V_{g1}, V_{g2})$  of (0, 1) and (1, 0) give an "off" current ratio is more than  $10^2$ .

The XOR operation is achieved by applying the next half Coulomb oscillation square against  $V_{g1}$ , that is, two  $V_{g1}$  input levels of  $\Delta V_{g1}/2$  and  $\Delta V_{g1}$  as "0" and "1" and two  $V_{g2}$  input levels of  $V_{g2}'$  and  $V_{g2}' + \Delta V_{g2}/2$  as "0" and "1," respectively (red solid line in Figure 4c). It can be seen that the on/off current ratio for the XOR operation is the same as that for the XNOR operation, 10<sup>2</sup>; the reason for being is that the double-gate SET exhibits ideally periodic Coulomb oscillation against

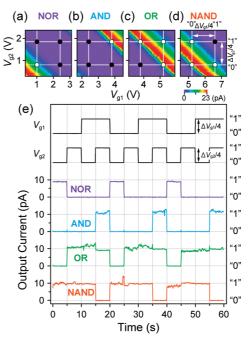

Figure 5. Plot of 2D output current for quarter Coulomb oscillation squares versus  $V_{g1}$  and  $V_{g2}$  for (a) NOR, (b) AND, (c) OR, and (d) NAND operations at  $V_d = 20$  mV. The open circles (10 pA) and closed circles (0.2 pA or less) represent the combination of the gate operation points. (e) Logic operation of NOR, AND, OR, NAND gates for two input pulses. The height of the input pulse for gate 1 (2) is  $\Delta V_{g1}/4$  ( $\Delta V_{g2}/4$ ). In the cases of the NOR, AND, OR, and NAND operations, the origin point of  $V_{g1}$  is shifted  $\Delta V_{g1}/4$  one by one and  $V_{g2}$  is a constant value of 0.80 V.

$V_{g1}$  and  $V_{g2}$ . These on/off ratios are larger than that of double-gate SETs fabricated by using silicon technology<sup>9–11</sup> or a CNT.<sup>12</sup>

The high periodicity of Coulomb oscillations of the fabricated double-gate SET enables not only the XNOR and XOR operations but also other two-input logic operations such as NOR, AND, OR, and NAND. The output current of 10 pA can be generated at  $V_d = 20$  mV by using both the positive and the negative slopes of a Coulomb oscillation peak with changing  $\Delta V_{g1}/4$  and  $\Delta V_{g2}/4$ , as shown in Figure 2.

Figure 5 panels a-d demonstrate NOR, AND, OR, and NAND operations by using guarter Coulomb oscillation squares. In Figure 5d, the NAND operation is explained as follows: Here,  $(V_{q1}", V_{q2}")$  of (5.2 V, 0.80 V) is taken as the origin of the input levels of (0, 0). Changing  $(V_{q1}, V_{q2})$  to three-quarter Coulomb oscillation squares  $(V_{q1}'', V_{q2}'')$ ,  $(V_{q1}'' + \Delta V_{q1}/4, V_{q2}'')$ , and  $(V_{a1}'', V_{a2}'' + \Delta V_{a2}/4)$ , corresponding to (0, 0), (1, 0), and (0, 1), respectively, results in an output current of 10 pA (on state). On the contrary, at ( $V_{g1}'' + \Delta V_{g1}/4$ ,  $V_{g2}'' +$  $\Delta V_{\rm q2}$ /4) of (1, 1), the output current becomes 0.2 pA or less (off state), i.e., the NAND operation. Figure 5e shows the actual output current for the NAND operation for two input pulses (orange solid line), where the height and offset of the input pulse are  $\Delta V_{q1}/4$ and  $V_{q1}^{"}$  for gate 1 and  $\Delta V_{q2}^{'}$  and  $V_{q2}^{"}$  for gate 2, respectively.

VOL.6 • NO.3 • 2798-2803 • 2012

Figure 5 panels a-c show the next three-quarter Coulomb oscillation squares against  $V_{a1}$ , where the origins of the input levels are  $(V_{g1}" - 3\Delta V_{g1}/4, V_{g2}")$ ,  $(V_{g1}'' - 2\Delta V_{g1}/4, V_{g2}'')$ , and  $(V_{g1}'' - \Delta V_{g1}/4, V_{g2}'')$ , respectively; accordingly, the logic operations of the fabricated two-gate SET become NOR, AND, and OR, respectively, from the NAND operation. Figure 5e also shows the output currents for the NOR, AND, and OR operations for two input pulses (purple, blue, and green solid lines, respectively); here, the heights of the input pulses for gates 1 and 2 are  $\Delta V_{q1}/4$  and  $\Delta V_{a2}/4$ , respectively. The levels of output current in the off states for NOR, AND, OR, and NAND are the same as those for XNOR and XOR-0.2 pA or less. This observation indicates that our fabricated SET can have versatile logic operations with the same output property. These logic operations are expected to be available at room temperature if we use smaller NPs such as 2 nm in the core diameter.<sup>23</sup> For the ideal logic operations, the gatecapacitance ratio of  $C_{g1}/C_{g2}$  should be 1. In the present experiment, it is 0.74. As the value of the gate capacitance strongly depends on the SET structures consisting of NP, source/drain electrodes and two side gate

electrodes, the shape of nanogap electrodes is a key issue to obtain the gate-capacitance ratio of 1. As the position of NP is almost center of nanogap electrodes in the present SET, the gate-capacitance ratio will be improved by narrowing the width of the nanogap electrodes.

#### CONCLUSION

We have chemically assembled double-gate SET by using electroless gold-plated nanogap electrodes and chemisorbed chemically synthesized gold nanoparticles. The SET exhibits more than three cycles of Coulomb diamonds under changing bias voltages of both the gates without any distortion or hysteresis, and the electron transfer properties of the SET are highly stable during the operation period (more than a week) at 9 K. Phase shift of the Coulomb oscillation according to a linear combination of the gate voltages gives XOR and XNOR operations with an on/off current ratio of  $10^2$ . Furthermore, the NAND, OR, NOR, and AND operations are achieved using the same SET. Owing to the stability of the fabricated SET, it is expected to be useful in applications requiring versatile logic gate operations with high precision and stability.

#### **METHODS**

The overall chemical assembling processes of SET fabrication are shown in the previous reports.<sup>13–15</sup> Preliminary source and drain electrodes with two side gates were fabricated on a Si/SiO<sub>2</sub> substrate by electron beam lithography (EBL) and lift-off, with the gap between the source and the drain kept at  $\sim$ 25 nm. Although these preliminary electrodes were prepared by the top-down approach of EBL, subsequent fabrication was done using the bottom-up approach, wherein the SET was fabricated only to immerse the substrate into various solutions. The nanogap electrodes were then fabricated by electroless gold plating using iodine tincture,<sup>19</sup> where the gap was controlled by tuning the plating time. In this study, we maintained a gap of about 10 nm between the source and drain electrodes (see Figure 1a); this gap is large enough for introducing into it a decanethiol-protected Au NP with diameter of about 9 nm (core diameter of 6.2  $\pm$  0.8 nm), which was chemically synthesized.<sup>16</sup> A Coulomb island was introduced in the following three steps: (1) an octanethiol self-assembled monolayer (SAM) was formed on the surface of the electrodes, (2) decanedithiol was introduced into the SAM, and (3) the decanethiol-protected Au NP was chemisorbed via decanedithiol (see Figure 1b).<sup>17,18</sup>

Experimental setup measuring electron transport properties of SET is also same as the previous work.  $^{\rm 15}$

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. We thank M. Miyakawa for providing technical support in SEM observations. This study was partially supported by a Grant-in-Aid for Scientific Research on Innovative Areas (No. 20108011,  $\pi$ -Space) from the Ministry of Education, Culture, Sports, Science and Technology (MEXT), Japan; by a Grant-in-Aid for Scientific Research (A) (23245028) from MEXT (T.T.); by a Grant-in-Aid for the Japan Society for the Promotion of Science (JSPS) Fellows, MEXT (S.K.); by the Global COE Program of "Photonics Integration-Core Electronics," MEXT; by the Collaborative Research Project of Materials and Structures Laboratory, Tokyo Institute of Technology; and by the World

Class University (WCU) Program through the Ministry of Education, Science and Technology of Korea (R31-10022).

#### **REFERENCES AND NOTES**

- Likharev, K. K. Single-Electron Devices and Their Applications. Proc. IEEE 1999, 87, 606–632.

- Yano, K.; Ishii, T.; Sano, T.; Mine, T.; Murai, F.; Hashimoto, T.; Kobayashi, T.; Kure, T.; Seki, K. Single-Electron Memory for Giga-to-Tera Bit Storage. *Proc. IEEE* **1999**, *87*, 633–651.

- Ono, Y.; Fujisawa, A.; Nishiguchi, K.; Inokawa, H.; Takahashi, Y. Manipulation and Detection of Single Electrons for Future Information Processing. J. Appl. Phys. 2005, 97, 031101.

- Ishibashi, K; Moriyama, S.; Tsuya, D.; Fuse, T.; Suzuki, M. Quantum-Dot Nanodevices with Carbon Nanotubes. J. Vac. Sci. Technol. 2006, 24, 1349–1355.

- Zabet-Khosousi, A.; Dhirani, A.-A. Charge Transport in Nanoparticle Assemblies. *Chem. Rev.* 2008, 108, 4072–4124.

- Uchida, K.; Koga, J.; Ohba, R.; Toriumi, A. Programmable Single-Electron Transistor Logic for Future Low-Power Intelligent LSI: Proposal and Room-Temperature Operation. *IEEE Trans. Electron Devices* **2003**, *50*, 1623–1630.

- Schoelkopf, R. J.; Wahlgren, P.; Kozhevnikov, A. A.; Delsing, P.; Prober, D. E. The Radio-Frequency Single-Electron Transistor (RF-SET): A Fast and Ultrasensitive Electrometer. *Science* 1998, 280, 1238–1242.

- Tucker, J. R. Complementary Digital Logic Based on the "Coulomb Blockade". J. Appl. Phys. 1992, 72, 4399–4413.

- Takahashi, Y.; Fujiwara, A.; Yamazaki, K.; Namatsu, H.; Kurihara, K.; Murase, K. Multigate Single-Electron Transistors and Their Application to an Exclusive-OR Gate. *Appl. Phys. Lett.* **2000**, *76*, 637–639.

- Kitade, T.; Ohkura, K.; Nakajima, A. Room-Temperature Operation of an Exclusive-OR Circuit Using a Highly Doped Si Single-Electron Transistor. *Appl. Phys. Lett.* 2005, *86*, 123118.

- Kim, S.-J.; Lee, C.-K.; Chung, R.-S.; Park, E.-S.; Shin, S.-J.; Choi, J.-B.; Yu, Y.-S. Single-Electron-Based Flexible Multivalued Exclusive-OR Logic Gate. *IEEE Trans. Electron Devices* 2009, 56, 1048–1055.

- Tsuya, D.; Suzuki, M.; Aoyagi, Y.; Ishibashi, K. Exclusive-OR Gate Using a Two-Input Single-Electron Transistor in Single-Wall Carbon Nanotubes. *Appl. Phys. Lett.* 2005, *87*, 153101.

- Azuma, Y.; Yasutake, Y.; Kono, K.; Kanehara, M.; Teranishi, T.; Majima, Y. Single-Electron Transistor Fabricated by Two Bottom-Up Processes of Electroless Au Plating and Chemisorption of Au Nanoparticle. *Jpn. J. Appl. Phys.* 2010, 49, 090206.

- Azuma, Y.; Suzuki, S.; Maeda, K.; Okabayashi, N.; Tanaka, D.; Sakamoto, M.; Teranishi, T.; Buitelaar, M. R.; Smith, C. G.; Majima, Y. Nanoparticle Single-Electron Transistor with Metal-Bridged Top-Gate and Nanogap Electrodes. *Appl. Phys. Lett.* **2011**, *99*, 073109.

- Okabayashi, N.; Maeda, K.; Muraki, T.; Tanaka, D.; Sakamoto, M.; Teranishi, T.; Majima, Y. Uniform Charging Energy of Single-Electron Transistors by Using Size-Controlled Au Nanoparticles. *Appl. Phys. Lett.* **2012**, *100*, 033101.

- Teranishi, T.; Hasegawa, S.; Shimizu, T.; Miyake, M. Heat-Induced Size Evolution of Gold Nanoparticles in the Solid State. *Adv. Mater.* 2001, *13*, 1699–1701.

- Li, X.; Yasutake, Y.; Kono, K.; Kanehara, M.; Teranishi, T.; Majima, Y. Au Nanoparticles Chemisorbed by Dithiol Molecules Inserted in Alkanethiol Self-Assembled Monolayers Characterized by Scanning Tunneling Microscopy. *Jpn. J. Appl. Phys.* **2009**, *48*, 04C180.

- Morita, T.; Lindsay, S. Determination of Single Molecule Conductances of Alkanedithiols by Conducting-Atomic Force Microscopy with Large Gold Nanoparticles. J. Am. Chem. Soc. 2007, 129, 7262–7263.

- Yasutake, Y.; Kono, K.; Kanehara, M.; Teranishi, T.; Buitelaar, M. R.; Smith, C. G.; Majima, Y. Simultaneous Fabrication of Nanogap Gold Electrodes by Electroless Gold Plating Using a Common Medical Liquid. *Appl. Phys. Lett.* **2007**, *91*, 203107.

- 20. Durrani, Z. A. K. Single-Electron Devices and Circuits in Silicon; Imperial College: London, 2009; Chapter 2.

- 21. Hanna, A. E.; Tinkham, M. Variation of the Coulomb Staircase in a Two-Junction System by Fractional Electron Charge. *Phys. Rev. B* **1991**, *44*, 5919–5922.

- Zhang, H.; Yasutake, Y.; Shichibu, Y.; Teranishi, T.; Majima, Y. Tunneling Resistance of Double-Barrier Tunneling Structures with an Alkanethiol-Protected Au Nanoparticle. *Phys. Rev. B* 2005, *72*, 205441.

- Kano, S.; Azuma, Y.; Kanehara, M.; Teranishi, T.; Majima, Y. Room-Temperature Coulomb Blockade from Chemically Synthesized Au Nanoparticles Stabilized by Acid–Base Interaction. *Appl. Phys. Express* **2010**, *3*, 105003.

- Bolotin, K. I.; Kuemmeth, F.; Pasupathy, A. N.; Ralph, D. C. Metal-Nanoparticle Single-Electron Transistors Fabricated Using Electromigration. *Appl. Phys. Lett.* **2004**, *84*, 3154– 3456.

- Kuemmeth, F.; Bolotin, K. I.; Shi, S.-F.; Ralph, D. C. Measurement of Discrete Energy-Level Spectra in Individual Chemically Synthesized Gold Nanoparticles. *Nano Lett.* 2008, *8*, 4506–4512.

- Ray, V.; Subramanian, R.; Bhadrachalam, P.; Ma, L.-C.; Kim, C.-U.; Koh, S. J. CMOS-Compatible Fabrication of Room-Temperature Single-Electron Devices. *Nat. Nanotechnol.* 2008, *3*, 603–608.

- Khondaker, S. I.; Luo, K.; Yao, Z. The Fabrication of Single-Electron Transistors Using Dielectrophoretic Trapping of Individual Gold Nanoparticles. *Nanotechnology* **2010**, *21*, 095204.

- Danilov, A. V.; Golubev, D. S.; Kubatkin, S. E. Tunneling Through a Multigrain System: Deducing Sample Topology from Nonlinear Conductance. *Phys. Rev. B* 2002, 65, 125312.

- Sato, T.; Ahmed, H.; Brown, D.; Johnson, B. F. G. Single Electron Transistor Using a Molecularly Linked Gold Colloidal Particle Chain. J. Appl. Phys. **1997**, 82, 696–701.

- Noguchi, Y.; Terui, T.; Katayama, T.; Matsushita, M. M.; Sugawara, T. Superperiodic Conductance in a Molecularly Wired Double-Dot System Self-Assembled in a Nanogap Electrode. J. Appl. Phys. 2010, 108, 094313.